P2020NXE2KFC माइक्रोप्रोसेसरहरू MPU P2020E ET १०००/६६७ R2.1

♠ उत्पादन विवरण

| उत्पादन विशेषता | विशेषता मान |

| निर्माता: | NXP ले |

| उत्पादन कोटी: | माइक्रोप्रोसेसरहरू - MPU |

| ढुवानी प्रतिबन्धहरू: | यो उत्पादनलाई संयुक्त राज्य अमेरिकाबाट निर्यात गर्न थप कागजातहरू आवश्यक पर्न सक्छ। |

| RoHS: | विवरणहरू |

| माउन्टिङ शैली: | एसएमडी/एसएमटी |

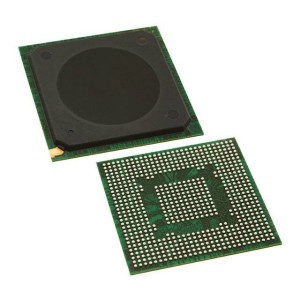

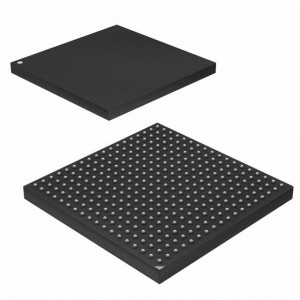

| प्याकेज / केस: | PBGA-689 को लागि सोधपुछ पेश गर्नुहोस्, हामी तपाईंलाई 24 घण्टामा सम्पर्क गर्नेछौं। |

| शृङ्खला: | पी२०२० |

| कोर: | e500-v2 का थप वस्तुहरू |

| कोरहरूको संख्या: | २ कोर |

| डाटा बस चौडाइ: | ३२ बिट |

| अधिकतम घडी आवृत्ति: | १ गिगाहर्ज |

| L1 क्यास निर्देशन मेमोरी: | ३२ केबी |

| L1 क्यास डेटा मेमोरी: | ३२ केबी |

| सञ्चालन आपूर्ति भोल्टेज: | १.०५ वी |

| न्यूनतम सञ्चालन तापक्रम: | - ४० डिग्री सेल्सियस |

| अधिकतम सञ्चालन तापक्रम: | + १२५ डिग्री सेल्सियस |

| प्याकेजिङ: | ट्रे |

| ब्रान्ड: | NXP अर्धचालकहरू |

| I/O भोल्टेज: | १.५ वी, १.८ वी, २.५ वी, ३.३ वी |

| निर्देशन प्रकार: | तैरने बिन्दु |

| इन्टरफेस प्रकार: | इथरनेट, I2C, PCIe, SPI, UART, USB |

| L2 क्यास निर्देशन / डेटा मेमोरी: | ५१२ केबी |

| मेमोरी प्रकार: | L1/L2 क्यास |

| आर्द्रता संवेदनशील: | हो |

| I/O को संख्या: | १६ इन्पुट/आउट |

| प्रोसेसर शृङ्खला: | QorIQName |

| उत्पादन प्रकार: | माइक्रोप्रोसेसरहरू - MPU |

| कारखाना प्याक मात्रा: | 27 |

| उपश्रेणी: | माइक्रोप्रोसेसरहरू - MPU |

| व्यापारिक नाम: | QorIQName |

| वाचडग टाइमरहरू: | वाचडग टाइमर छैन |

| भाग # उपनामहरू: | ९३५३१९६५९५५७ |

| एकाइ तौल: | ०.१८५०९० औंस |

निम्न सूचीले P2020 सुविधाको सिंहावलोकन प्रदान गर्दछ।सेट:

• दोहोरो उच्च-प्रदर्शन पावर आर्किटेक्चर® e500 कोर।

• ३६-बिट भौतिक ठेगाना

- दोहोरो-परिशुद्धता फ्लोटिंग-पोइन्ट समर्थन

- ३२-केबाइट L1 निर्देशन क्यास र ३२-केबाइट L1 डेटाप्रत्येक कोरको लागि क्यास

- ८००-मेगाहर्ट्ज देखि १.३३-गेगाहर्ट्ज घडी आवृत्ति

• ECC सहितको ५१२ Kbyte L2 क्यास। साथै कन्फिगर योग्यSRAM र स्ट्यासिङ मेमोरी।

• तीन १०/१००/१००० Mbps बढाइएको तीन-गति इथरनेटनियन्त्रकहरू (eTSECs)

- TCP/IP त्वरण, सेवाको गुणस्तर, र

वर्गीकरण क्षमताहरू

– IEEE Std १५८८™ समर्थन

- हानिरहित प्रवाह नियन्त्रण

– आर/जी/एमआईआई, आर/टीबीआई, एसजीएमआईआई

• विभिन्न मल्टिप्लेक्सिङलाई समर्थन गर्ने उच्च-गति इन्टरफेसहरूविकल्पहरू:

- ३.१२५ GHz सम्मका चार SerDes मल्टिप्लेक्समानियन्त्रकहरू

- तीन PCI एक्सप्रेस इन्टरफेसहरू

- दुई सिरियल RapidIO इन्टरफेसहरू

- दुई SGMII इन्टरफेसहरू

• उच्च गतिको USB नियन्त्रक (USB २.०)

- होस्ट र उपकरण समर्थन

- परिष्कृत होस्ट नियन्त्रक इन्टरफेस (EHCI)

- PHY मा ULPI इन्टरफेस

• परिष्कृत सुरक्षित डिजिटल होस्ट नियन्त्रक (SD/MMC)परिष्कृत सिरियल परिधीय इन्टरफेस (eSPI)

• एकीकृत सुरक्षा इन्जिन

- प्रोटोकल समर्थनमा SNOW, ARC4, 3DES, AES, समावेश छन्।RSA/ECC, RNG, एकल-पास SSL/TLS, कासुमी

- XOR त्वरण

• ६४-बिट DDR2/DDR3 SDRAM मेमोरी नियन्त्रक सहितECC समर्थन

• प्रोग्रामेबल इन्टरप्ट कन्ट्रोलर (PIC) अनुरूपओपनपिक मानक

• दुई चार-च्यानल DMA नियन्त्रकहरू

• दुई I2C नियन्त्रकहरू, DUART, टाइमरहरू

• परिष्कृत स्थानीय बस नियन्त्रक (eLBC)

• १६ सामान्य-उद्देश्यीय I/O संकेतहरू

• सञ्चालन जंक्शन तापक्रम

• ३१ × ३१ मिमी ६८९-पिन WB-TePBGA II (तार बन्धन)(तापक्रम-बृद्धि गरिएको प्लास्टिक BGA)